© Marc COUSINEAU/LAPLACE/CNRS Images

Référence

20180009_0006

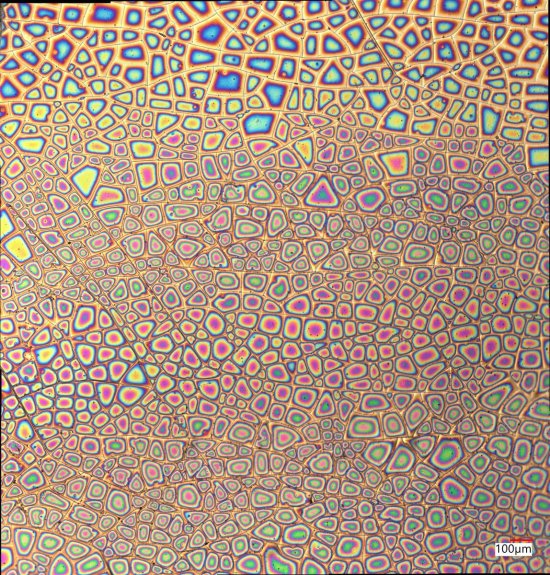

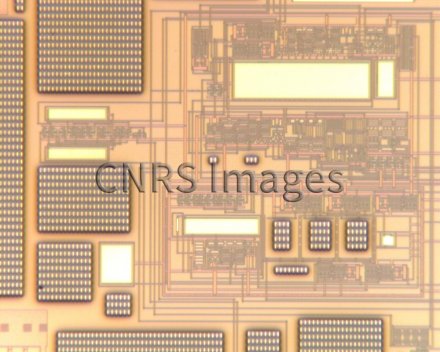

Circuit intégré réalisé dans une technologie submicromètreique CMOS

Circuit intégré réalisé dans une technologie submicromètreique (inférieure à un micromètre) CMOS (Complementary metal oxide semiconductor) implémentant des électroniques analogiques Large-bande, Basses-tensions (300MHz, 5V) (laboratoire LAPLACE). Des amplificateurs opérationnels, conçus à partir de transistors de petites tailles (0.35 x 1 µm² en pratique) et de capacités de faibles valeurs (0.5 à 3 pF, carrés jaunes sur la figure), s'y trouvent. Ils servent à amplifier une différence de potentiel électrique présente à leurs entrées. Cette électronique permet de réaliser une fonction d’auto-entrelacement des signaux de commande d’un convertisseur multiphasé.

L’utilisation des médias visibles sur la Plateforme CNRS Images peut être accordée sur demande. Toute reproduction ou représentation est interdite sans l'autorisation préalable de CNRS Images (sauf pour les ressources sous licence Creative Commons).

Aucune modification d'une image ne peut être effectuée sans l'accord préalable de CNRS Images.

Aucune utilisation à des fins publicitaires ou diffusion à un tiers d'une image ne peut être effectuée sans l'accord préalable de CNRS Images.

Pour plus de précisions consulter Nos conditions générales